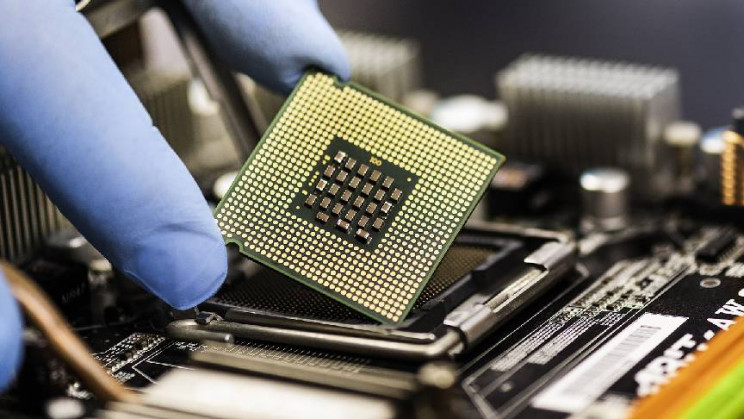

หลังจากที่เมื่อเดือนพฤษภาคมที่ผ่านมาทีมนักวิจัยจาก MIT, มหาวิทยาลัยแห่งชาติของไต้หวันและ TSMC ผู้ผลิตชิปรายใหญ่จากไต้หวันได้ประกาศความสำเร็จในการพัฒนาวิธีการผลิตชิปที่จะทำให้สามารถทลายกำแพงการผลิตชิปให้มีขนาดเล็กลงกว่า 1 นาโนเมตรได้โดยการใช้ semi-metal bismuth ในการผลิตชิป (ปัจจุบันเทคโนโลยีการผลิตชิปประมวลผลได้เล็กลงมาถึงระดับ 3 นาโนเมตรแต่ก็ยังคงติดกำแพงใหญ่ที่ทำให้สามารถผลิตชิปที่มีขนาดเล็กลงไปได้อีก)

มาวันนี้ซัมซุงก็ได้จับมือ IBM ในการร่วมพัฒนาอีกไอเดียในการเพิ่มประสิทธิภาพให้กับชิปประมวลผลโดยไม่ต้องลดขนาดเทคโนโลยีในการผลิต แต่อาศัยการซ้อนชั้นของตัวนำที่ใช้ทำแผงวงจรเพื่อเพิ่มประสิทธิภาพของชิป เทคนิคนี้เรียกว่า Vertical Transport Field Effect Transistors (VTFET) ซึ่งจำทำให้กระแสไฟฟ้าสามารถวิ่งในวงจรในแนวดิ่งแบบ 3 มิติได้จากเดิมที่วิ่งอยู่บนแผ่นแผงวงจรระนาบ 2 มิติ ช่วยลดระยะทางการวิ่งของกระแสไฟฟ้าในวงจรทำให้ตัวชิปมีประสิทธิภาพในการประมวลผลที่ดีขึ้นและมีอัตราการใช้พลังงานที่ลดน้อยลงด้วย

จากรายงานเทคนิคนี้จะช่วยเพิ่มประสิทธิภาพการประมวลผลของชิปได้เป็นเท่าตัว หรือสามารถนำมาประยุกต์ใช้เพื่อลดการใช้พลังงานของตัวชิปลงได้กว่า 85% เมื่อเทียบกับการออกแบบชิปแบบแผ่นเรียบ(FinFET transistors)ที่ใช้อยู่เดิม โดยทีมนักพัฒนาเชื่อว่าด้วยเทคโนโลยีการผลิตแบบใหม่นี้จะทำให้สมาร์ทโฟนที่ใช้ในอนาคตจะสามารถใช้งานได้นานเป็นสัปดาห์ต่อการชาร์จไฟเต็ม เมื่อเทียบกับที่ใช้ได้ไม่เต็มวันดีอย่างในปัจจุบัน

ซึ่งไม่ใช่แต่ซัมซุงกับ IBM เท่านั้น แม้แต่ Intel ผู้ผลิตชิปประมวลผลเจ้าใหญ่ของโลกก็มีความสนใจพัฒนาเทคโนโลยีการผลิตชิปแบบซ้อนแผ่นวงนี้จรเช่นเดียวกัน

ก็คงต้องติดตามดูกันว่าใครจะเป็นเจ้าแรกที่สามารถนำเทคโนโลยีการผลิตแบบใหม่นี้มาใช้ในการผลิตชิปเพื่อสร้างข้อได้เปรียบในการแข่งขันในตลาดชิปที่นับวันจะมีความต้องการพุ่งสูงขึ้น

***************************************************************************************************************

อ้างอิง:

https://www.reuters.com/technology/intel-shows-research-packing-more-computing-power-into-chips-beyond-2025-2021-12-11/

https://interestingengineering.com/samsung-ibm-could-break-1nm-threshold-in-chips-with-stacked-transistors